Новое поступление

Мини видеокамера регистратор с креплением к 328 мини 3 V/8 M 5V/16M ATMEGA328 ATMEGA328P AU МГц 5V/16

IRL3502 220 20V 110A|Аксессуары для демонстрационных стендов| |

2 комплекта модуля для Arduino: 1 Набор UNO R3 ATmega328P CH340 USB плата DIY и комплект синий черный

Генератор сигналов AD9833 DDS треугольная Синусоидальная волна программируемый

Гибкий дисплей E Ink Raw 2 13 дюйма 212x104 черный/белый двухцветный интерфейс SPI без PCB

Цифровой термостат плата контроллера температуры с реле 20 А светодиодный

Плата адаптера PCIe M.2 к SATA3.0 плата расширения работает с демо платой Firefly RK3399|pcie

Характеристики

Для макетной платы USB макетная плата USB3.0 FPGA + EP4CE10 камера|Аксессуары для

История изменения цены

*Текущая стоимость 7 649,02 уже могла изменится. Что бы узнать актуальную цену и проверить наличие товара, нажмите "Добавить в корзину"

| Месяц | Минимальная цена | Макс. стоимость | Цена |

|---|---|---|---|

| Mar-03-2026 | 9714.17 руб. | 9908.24 руб. | 9811 руб. |

| Feb-03-2026 | 7878.94 руб. | 8036.15 руб. | 7957 руб. |

| Jan-03-2026 | 9561.42 руб. | 9752.73 руб. | 9656.5 руб. |

| Dec-03-2025 | 9485.66 руб. | 9675.69 руб. | 9580 руб. |

| Nov-03-2025 | 7573.67 руб. | 7724.44 руб. | 7648.5 руб. |

| Oct-03-2025 | 9332.40 руб. | 9519.22 руб. | 9425.5 руб. |

| Sep-03-2025 | 9255.85 руб. | 9440.24 руб. | 9347.5 руб. |

| Aug-03-2025 | 9179.80 руб. | 9363.35 руб. | 9271 руб. |

Описание товара

Дорогие друзья! У нас есть

1. Макетная плата USB2.0, разработанная liangko (FPGA + 2SDRAM + USB2.0), имеет разумную двойную буферную структуру SDRAM. Данные, адрес и линия управления двух sdrams полностью независимы, что более подходит для работы буфера пинг-понга.

2, плата два SDRAM, SDRAM контроллер VHDL исходный код (не niios исходный код).

3. Входная часть сигнала принимает дизайн открытого интерфейса. Разъем на левой стороне печатной платы составляет 26 контактов (включая источник питания и заземление, а остальное-24 IO).

4, для инженерных приложений, разработка платы, соответствующие синхронным SLAVE FIFO высокоскоростной передачи, все формы исходного кода, могут быть использованы, не нужно учиться, вторичное развитие.

5. Четырехслойная конструкция платы, независимый слой мощности и слой, более стабильный сигнал.

6. Цена составляет всего 378 юаней, макетная плата USB2.0 с высокой производительностью затрат.

7. Предоставьте верхний исходный код драйвера компьютера.

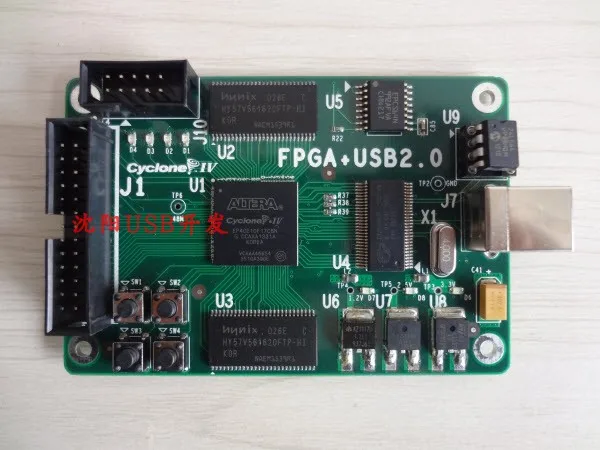

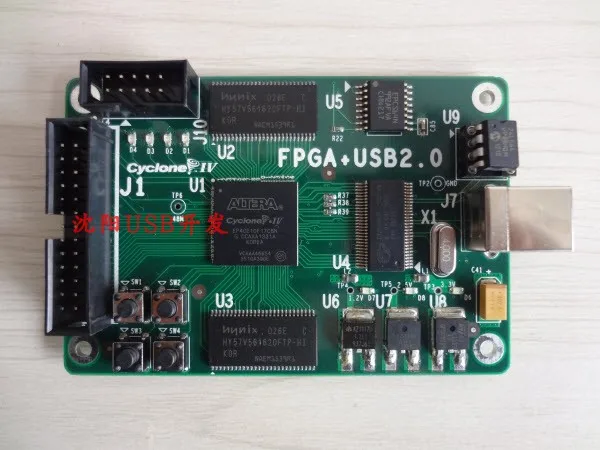

Передняя часть платы развития выглядит следующим образом:

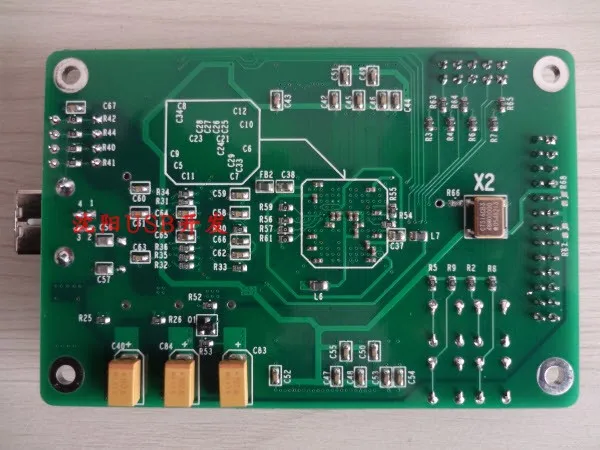

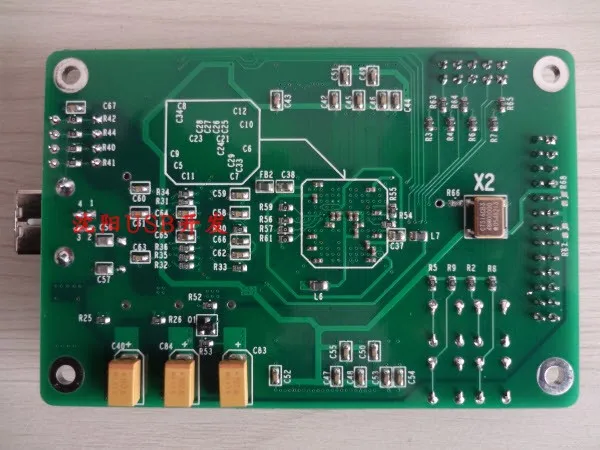

Обратная сторона платы развития выглядит следующим образом:

1. Аппаратные ресурсы на плате развития следующие:

Чип CY7C68013, соответствующий спецификации USB2.0, высокоскоростной протокол передачи 480 Мбит/с;

Через «панель управления», непосредственно записывает программу прошивки USB;

FPGA напрямую подключает две части SDRAM для завершения работы в пинг-понге и настройки кэша данных.

Две части SDRAM большой емкости, каждая с 128 Мбит, в общей сложности 256 Мбит.

FPGA принимает дизайн вертикальной совместимости, и пользователи могут заменить FPGA (EP2C5aEP2C8).

FPGA предоставляет JTAG и как интерфейс загрузки;

Один большой EPCS16;

Четыре СВЕТОДИОДНЫЙ, четыре кнопки, удобно для отладки;

Большая емкость источника питания дизайн, 3,3 v Ток 3A, удобный (с учётом движения автомобиля опорной семян пластин.

Все процедуры без брони, все исходные коды, включая верхнюю компьютерную программу;

Ii. Совет по развитию поддерживает следующие процедуры:

1. Первый пример, my_first_fpga

2. Второй slave_fifo_sync

3. Третий обычный Vend_ax

4. Обычная Отправка данных на печатную плату

5. Bulkloop пятого рутина

Iii. Поддержка верхней компьютерной программы:

Эта часть содержимого и 278 юаней, системная плата развития 378 юаней с хост-компьютером, чтобы отправлять данные в обычную схему.

Характеристическая вязкость полимера. Руководство по разработке платы развития:

В настоящее время, пожалуйста, обратитесь к Руководству по разработке пользователей платы развития 378 юаней.

5. Подходит для следующих применений:

Применение датчика, например, мобильный телефон и камера

Цифровой видеокамеры

Цифровые фотоаппараты;

Принтеры (принтеры)

Микшерный сканер (сканеры)

Видео устройства видеозахвата

Тесты и измерительное оборудование

Камеры видеонаблюдения;

Смотрите так же другие товары: