Новое поступление

Датчик ABS для 2005 01 Dodge Caravan/Grand Caravan Chrysler Town & кантри Караван/Grand Caravan/Town OE no.4683471AB|sensor

Фотоловушка для микроволновых систем радар 24 ГГц датчик радара FMK24E5100 FMK24E5110 FMK24E5200

Датчик положения дроссельной заслонки для грузовика VOLVO 20504685 1063332 3171530 5

Hi3520dv300 (Nvp6124b) Hd видео макетная плата основная плата|Датчик ABS| |

Абсолютно Новый настоящий синий Заглушка заднего колеса ABS Датчик скорости 4545A0

Ремонтные комплекты катушки зажигания для Mercedes S600 SL500 SL600 CL500 CL600 E420 S420 S500

Обмотку электродвигателя температуры датчик PTC термистор MZ6 120ES одна

BETTERSHENGSUN Store

Магазина BETTERSHENGSUN Store работает с 30.05.2019. его рейтинг составлет 83.01 баллов из 100. В избранное добавили 1724 покупателя. Средний рейтинг торваров продавца 4.3 в продаже представленно 25593 наименований товаров, успешно доставлено 2213 заказов. 836 покупателей оставили отзывы о продавце.

Характеристики

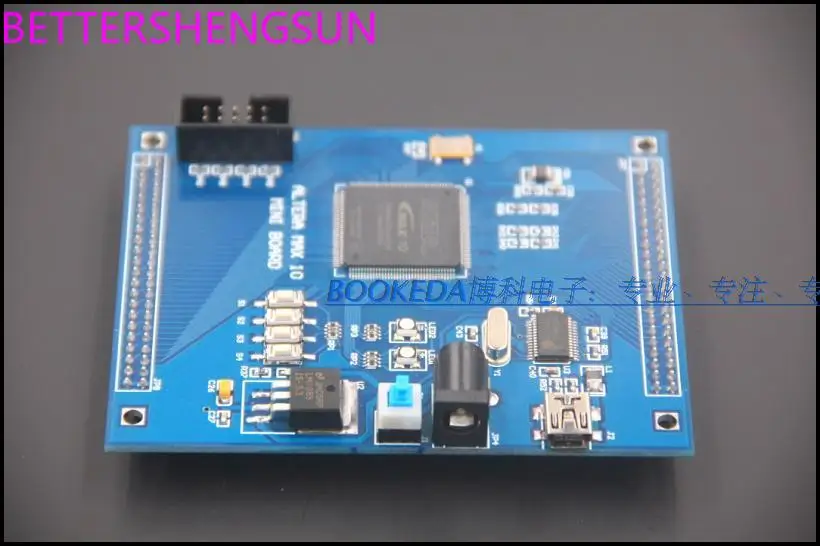

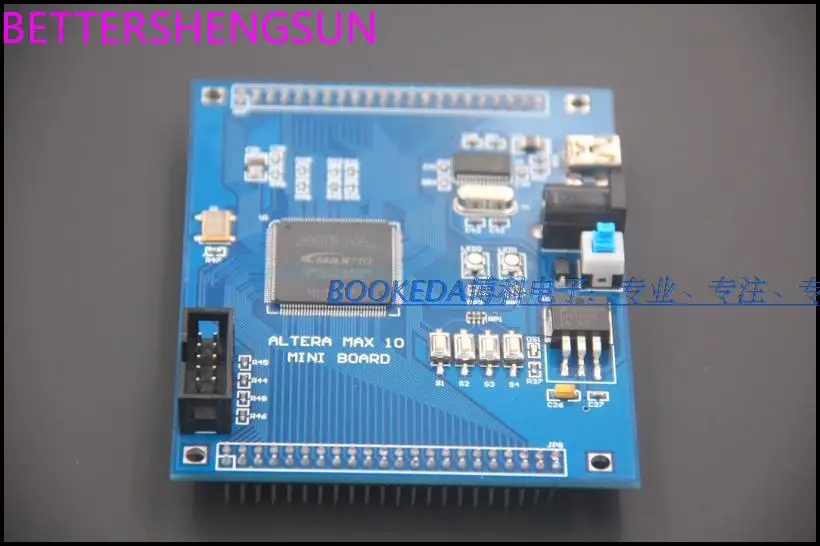

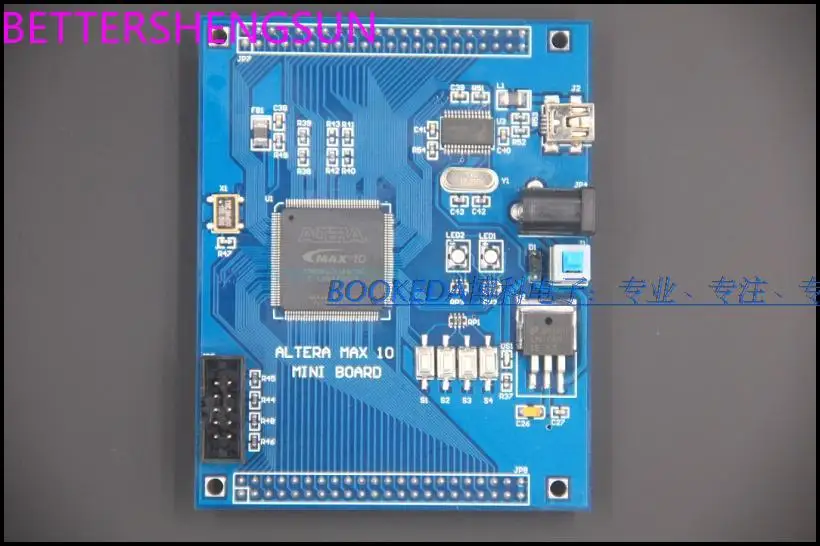

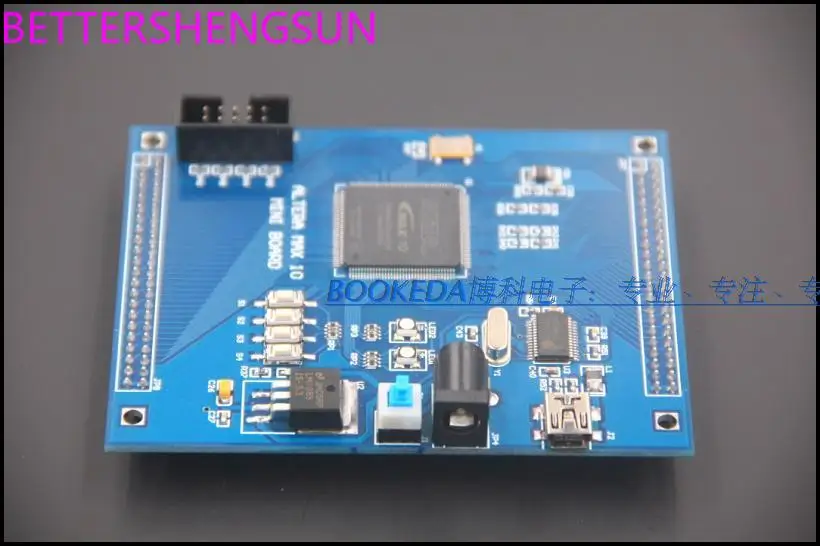

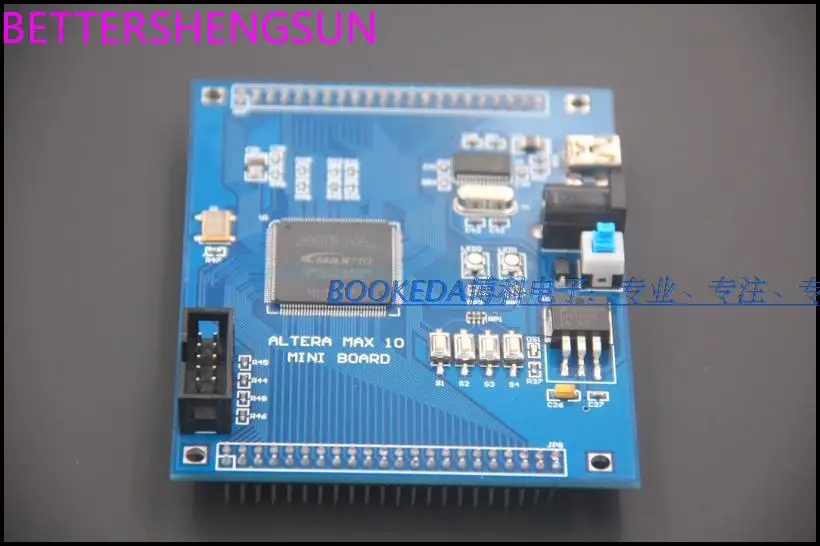

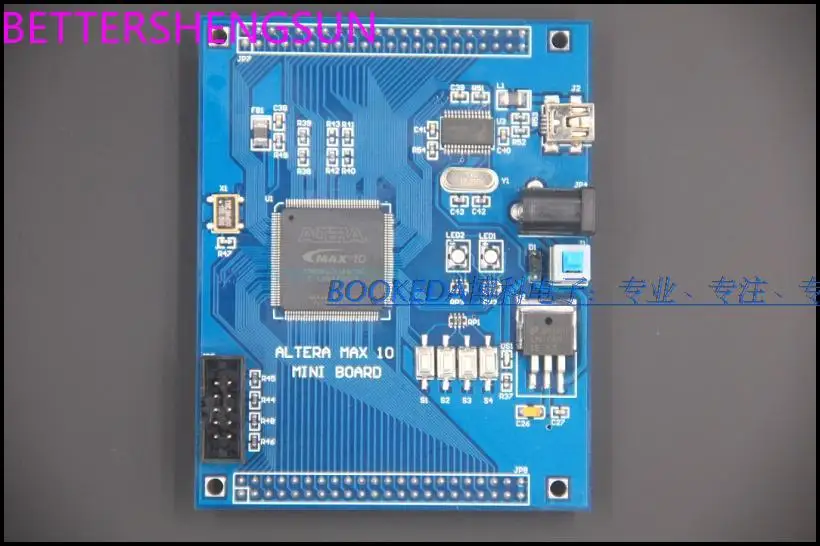

Altera ПЛИС MAX 10 FPGA CPLD экспериментировать макетная плата Системы доска эксперимент

История изменения цены

*Текущая стоимость 5 896,27 уже могла изменится. Что бы узнать актуальную цену и проверить наличие товара, нажмите "Добавить в корзину"

| Месяц | Минимальная цена | Макс. стоимость | Цена |

|---|---|---|---|

| Apr-06-2026 | 7016.92 руб. | 7367.34 руб. | 7191.5 руб. |

| Mar-06-2026 | 6957.25 руб. | 7305.69 руб. | 7131 руб. |

| Feb-06-2026 | 5837.50 руб. | 6129.64 руб. | 5983 руб. |

| Jan-06-2026 | 6839.75 руб. | 7181.44 руб. | 7010 руб. |

| Dec-06-2025 | 5955.70 руб. | 6253.10 руб. | 6104 руб. |

| Nov-06-2025 | 6721.53 руб. | 7057.17 руб. | 6889 руб. |

| Oct-06-2025 | 6662.1 руб. | 6995.22 руб. | 6828.5 руб. |

| Sep-06-2025 | 6604.59 руб. | 6934.22 руб. | 6769 руб. |

| Aug-06-2025 | 6545.16 руб. | 6872.65 руб. | 6708.5 руб. |

Описание товара

Altera MAX 10 FPGA CPLD опытная плата, системная плата

Введение в ресурсы Совета по развитию:

- FPGA: макс. 10 :10M08SCE144C8

- Серийный порт: PL2303 USB к специальному чипу последовательного порта.

- Пользовательский экспериментСветодиодный: 2 трехцветных полных цвета.

- Кнопка проверки пользователяКлюч: 4.

- Системные часы: Встроенные активные часы.

- Интерфейс отладки:JTAG

- Все контакты пользователя.

- Источник питания: использование LT1085 и других специальных чипов питания, внешний входной интерфейс DC5V

- Размер основной платы: 95 мм × 76 мм

Введение в макс. 10

Altera's MAX®10 FPGA реализует передовые функции обработки в недорогих, однокристальных, небольших фасованных программируемых логических устройствах и является революционным нелетучим интегрированным устройством. Унаследовал однокристальные характеристики предыдущего поколения серии устройств MAX, используя одноядерный или двухъядерный источник питания напряжения, его плотность колеблется от 2 к до 50 Кле. Серия Max 10 FPGA обеспечивает улучшенную упаковку небольших пластин (3 мм x 3 мм), а также большое количество упаковочных продуктов I O pin.

Макс. 10 FPGA изготовлен по технологии TSMC 55 нм встроенной или флэш-памяти и поддерживает функцию мгновенного подключения. Интегрированные функции включают аналого-цифровой преобразователь (ADC) и флеш-память двойной конфигурации, что позволяет хранить два изображения на одном чипе и динамически переключаться между изображениями. В отличие от CPLD, MAX 10 FPGA также включает полнофункциональные FPGA функции, например,Nios®II Поддержка встроенного процессора с мягким сердечникомМодуль обработки цифрового сигнала (DSP) и контроллер памяти DDR3 с мягким сердечником.

Макс. 10 FPGA улучшает уровень интеграции компонентов системы, чтобы снизить затраты на уровень системы:

- Флеш-память двойной конфигурацииОсновная флэш-память поддерживает двойную конфигурацию и реализует тысячи перепрограммированных обновлений безопасности реального сбоя.

- Модуль моделированияИнтегрированная с ADC и датчиком температуры, функция выборки и сортировки очень гибкая, что сокращает задержку и уменьшает площадь печатной платы.

- Мгновенное соединение-Max10 FPGA является первым устройством, которое начинает работать на системной плате, управляя запуском других компонентов, таких как FPGA высокой плотности, ASIC, ASSP и процессор.

- Nios®II мягкое ядро встроенное processo-Max10 FPGA поддерживает интегрирование встроенного процессора Nios II Altera soft core, предоставляя встроенным разработчикам один чип, полностью настраиваемая мгновенная подсистема коммутационного процессора.

- Модуль DSPВ качестве первого нелетучего FPGA с DSP, MAX 10 FPGA очень подходит для высокопроизводительных и высокоточных приложений с интегрированным мультипликатором 18x18.

- Внешний интерфейс памяти DDR3-Max10fpga поддерживает DDR3 SDRAM и LPDDR2 интерфейсы через мягкий контроллер интеллектуальной собственности (IP) памяти, подходит для видео, передачи данных и встроенных приложений.

- Флэш-память пользователя-С функцией хранения флэш-кода памяти 736 КБ, макс. 10 FPGA поддерживает расширенные встроенные приложения Nios II с одним чипом. Емкость вспышки пользователя зависит от выбора конфигурации.

Упаковочный лист:

1.Основная плата

2.Один DVD (модуль рутинный, схематическая схема, руководство по данным, технические документы, программное обеспечение разработки и т. Д.)

3.Один высококачественный импульсный источник питания постоянного тока (5 В)

4. Линия передачи данных USB 1

Смотрите так же другие товары: